Husain Parvez · Habib Mehrez

# Application-Specific Mesh-based Heterogeneous FPGA Architectures

# Application-Specific Mesh-based Heterogeneous FPGA Architectures

# Application-Specific Mesh-based Heterogeneous FPGA Architectures

Husain Parvez

Université Pierre et Marie Curie

Paris VI, Laboratoire LIP6

Départment SoC, Equipe CIAN

4, Place Jussieu

75252 Paris

France

husainahmed154@hotmail.com

Habib Mehrez

Université Pierre et Marie Curie

Paris VI, Laboratoire LIP6

Départment SoC, Equipe CIAN

4, Place Jussieu

75252 Paris

France

habib.mehrez@lip6.fr

ISBN 978-1-4419-7927-8 e-ISBN 978-1-4419-7928-5 DOI 10.1007/978-1-4419-7928-5 Springer New York Dordrecht Heidelberg London

#### © Springer Science+Business Media, LLC 2011

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed is forbidden.

The use in this publication of trade names, trademarks, service marks, and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

#### Foreword

This book concerns the broad domain of reconfigurable architectures and more specifically FPGAs. Different issues that are the centre of this book are very essential and are intended to overcome the current limitations of FPGAs, which are experiencing extremely rapid and sustained development for several years. In fact, FPGAs offer a particularly remarkable flexibility but suffer from a level of performance that can be disadvantageous for some applications in terms of surface, speed or energy. This work presents several significant and original contributions in order to remove these limitations by focusing especially on surface metric.

This book aims at exploring heterogeneous FPGA architectures dedicated to a given set of application circuits. Beyond architecture exploration, this work also presents automatic FPGA "layout" generation flow, and a new component called as an ASIF "Application Specific Inflexible FPGA", which significantly reduces silicon footprint by customizing the architecture for a given set of applications circuits. The importance and originality of the contributions made in this work revolve around this new concept of application specific reconfigurable circuits, mainly the development of an entire design environment including: generation tools, floor-planning, placement and routing adapted to the case of heterogeneous blocks. Careful analysis of results and the validation of proposed techniques have also been observed.

The monograph of this book is based on Husain's doctoral thesis. It was a great pleasure for me to supervise his thesis. This book will be of special interest for students and researches in the domain of FPGA architectures in general, and application-specific FPGA architectures, heterogeneous FPGA architectures, and their automatic hardware generation in particular.

Prof. Dr. Habib MEHREZ Team Lead, Analog and Digital Integrated Circuit Group at System-on-Chip department of LIP6 Professor at University of Paris 6 (UPMC), Paris, France

#### **Preface**

#### 1 Abstract

Low volume production of FPGA-based products is quite effective and economical because they are easy to design and program in shortest possible time. The generic reconfigurable resources in an FPGA can be programmed to execute a vast variety of applications at mutually exclusive times. However, the flexibility of FPGAs makes them much larger, slower, and more power consuming than their counterpart ASICs. Consequently, FPGAs are unsuitable for applications requiring high volume production, high performance or low power consumption. The main theme of this work is to reduce area of FPGAs by introducing heterogeneous hard-blocks (such as multipliers, adders etc) in FPGAs, and by designing application specific FPGAs. Automatic FPGA layout generation techniques are employed to decrease non-recurring engineering (NRE) costs and time-to-market of application specific heterogeneous FPGA architectures.

This work initially presents a new environment for the exploration of mesh-based heterogeneous FPGA architectures. An architecture description mechanism allows to define new heterogeneous blocks. A variety of automatic and manual options can be selected to optimize floor-planning of heterogeneous blocks on the FPGA architecture. The exploration environment later allows to test different benchmark circuits on the newly defined heterogeneous FPGA architecture. An automatic FPGA layout generator is presented which generates a tile-based FPGA layout for a subset of architectures generated by our exploration environment. We have successfully taped-out a 1024 Look-Up Table based mesh FPGA architecture using 130nm 6-metal layer CMOS process of ST.

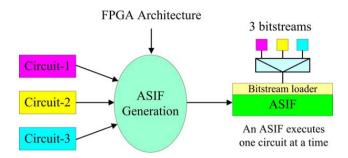

The Heterogeneous FPGA exploration environment is further enhanced to explore application specific FPGAs. If a digital product is required to provide multiple functionalities at exclusive times, each distinct functionality represented by an application circuit is efficiently mapped on an FPGA. Later, the FPGA is reduced for the given set of application circuits. This reduced FPGA is proposed and termed here as an Application Specific Inflexible FPGA (ASIF). The main idea is to perform prototyping, testing and even initial shipment of a design on an FPGA; later it can be migrated to an ASIF for high volume production. ASIF generation techniques can also be employed to generate a single configurable ASIC core that can perform multiple tasks at different times. An ASIF for 20 MCNC benchmark circuits is found to be 82% smaller than a traditional mesh-based unidirectional FPGA required to map any of these circuits. An ASIF can also be reprogrammed to execute new or modified circuits,

but unlike FPGAs, at a very limited scale. A new CAD flow is presented which can map new application circuits on an ASIF. An automatic ASIF hardware generator is also presented.

#### 2 Dedication

Dedicated to my parents, and to Scamoail, Hasan, Omer and Asma.

Husain Parvez

#### 3 Acknowledgments

This book is based on my PhD. thesis at LIP6/Universiy Pierre & Marie Curie (UPMC). I am highly indebted to Professor Habib Mehrez for supervising my thesis. I am also grateful for his continual technical advice. I am extremely thankful to Professor Guy Gogniat, and Dr. Gilles Sassatelli, for reviewing my thesis and for their valuable comments.

I am immensely grateful to Dr. Hayder Mrabet and Dr. Zied Marrakchi for providing detailed and insightful technical advice. This thesis would not had been possible without their support and guidance. I am also thankful to Dr. André Tissot and Dr. Nicolas Fel for their technical guidance in the tape-out of FPGA chip.

I would also like to thank Assosiate Professor Hassan Aboushady for motivating me to publish my PhD. work in the form of this book.

### Contents

| Fo | orewo | rd       |                                                               | v    |

|----|-------|----------|---------------------------------------------------------------|------|

| Pı | eface | !        |                                                               | vii  |

| Li | st of | Figures  | <b>3</b>                                                      | xiii |

| Li | st of | Tables   |                                                               | xvii |

| 1  | Intr  | oductio  | on                                                            | 1    |

|    | 1.1   | Backg    | ground                                                        | 1    |

|    |       | 1.1.1    | Microprocessors                                               | 2    |

|    |       | 1.1.2    | Application-specific instruction-set processor (ASIPs)        | 3    |

|    |       | 1.1.3    | Application Specific Integrated Circuits (ASICs)              | 3    |

|    |       | 1.1.4    | Structured-ASICs                                              | 4    |

|    | 1.2   | Motiv    | vation and contribution                                       | 4    |

|    |       | 1.2.1    | Exploration environment for heterogeneous FPGA Architectures  | 5    |

|    |       | 1.2.2    | Automatic FPGA layout generation                              | 5    |

|    |       | 1.2.3    | ASIF: Application Specific Inflexible FPGA                    | 6    |

|    |       | 1.2.4    | Automatic ASIF hardware generation                            | 6    |

|    | 1.3   | Field    | of Applications                                               | 7    |

|    | 1.4   | Book     | Organization                                                  | 7    |

| 2  | Stat  | e of the | e art                                                         | 9    |

|    | 2.1   | Introd   | duction to FPGAs                                              | 9    |

|    |       | 2.1.1    | Configurable Logic Block                                      | 10   |

|    |       | 2.1.2    | Routing Network                                               | 12   |

|    |       | 2.1.3    | Software Flow                                                 | 13   |

|    | 2.2   | Resea    | rch trends in FPGAs                                           | 17   |

|    |       | 2.2.1    | Versatile Packing, Placement and Routing, VPR                 | 19   |

|    |       | 2.2.2    | Madeo, a framework for exploring reconfigurable architectures | 20   |

|    |       | 2.2.3    | Altera Architecture                                           | 21   |

| X | Contents |

|---|----------|

| ^ | Comens   |

|   |      | 2.2.4 Altera HardCopy                                                        | 21 |

|---|------|------------------------------------------------------------------------------|----|

|   |      | 2.2.5 Configurable ASIC Cores (cASIC)                                        | 24 |

|   |      | 2.2.6 FPGA based processors                                                  | 24 |

|   |      | 2.2.7 A Reconfigurable Arithmetic Array for Multimedia Applications, CHESS 2 | 26 |

|   |      | 2.2.8 Reconfigurable Pipelined Data paths, Rapid                             | 26 |

|   |      | 2.2.9 Time-Multiplexed Signals                                               | 27 |

|   |      | 2.2.10 Time-Multiplexed FPGA                                                 | 28 |

|   | 2.3  | Conclusion                                                                   | 29 |

| 3 | Hete | erogeneous FPGA Exploration Environment                                      | 31 |

|   | 3.1  | Introduction and Previous Work                                               | 31 |

|   | 3.2  | Architecture Exploration Environment                                         | 32 |

|   | 3.3  | Architecture Description Mechanism                                           | 34 |

|   | 3.4  | Software Flow                                                                | 36 |

|   |      | 3.4.1 Parsers                                                                | 38 |

|   |      | 3.4.2 Placer                                                                 | 40 |

|   |      | 3.4.3 Router                                                                 | 45 |

|   | 3.5  | Floor-planning Techniques                                                    | 45 |

|   | 3.6  | Area Model                                                                   | 48 |

|   | 3.7  | Experimentation and Analysis                                                 | 48 |

|   |      | 3.7.1 Experimental Methodology using Common Architecture                     | 48 |

|   |      | 3.7.2 Benchmark Circuits for Common Architecture                             | 49 |

|   |      | 3.7.3 Results and Analysis for Common Architecture                           | 51 |

|   |      | 3.7.4 Experimental Methodology using Individual Architectures 5              | 56 |

|   |      | 3.7.5 Benchmark Circuits for Individual Architectures                        | 56 |

|   |      | 3.7.6 Results and Analysis for Individual Architectures                      | 56 |

|   | 3.8  | Conclusion                                                                   | 50 |

| 4 | FPG  | GA Layout Generation                                                         | 61 |

|   | 4.1  | Introduction and Previous work                                               | 51 |

|   | 4.2  | FPGA Generation                                                              | 52 |

|   |      | 4.2.1 Open-source VLSI tools                                                 | 53 |

|   |      | 4.2.2 Tile based approach                                                    | 54 |

|   |      | 4.2.3 Netlist generation                                                     | 55 |

|   |      | 4.2.4 Tile Layout                                                            | 56 |

|   |      | 4.2.5 Power routing                                                          | 66 |

|   |     |                                         | Contents | xi             |

|---|-----|-----------------------------------------|----------|----------------|

|   |     | 4.2.6 Clock generation                  |          | 66             |

|   |     | 4.2.7 Pin generation                    |          | 68             |

|   |     | 4.2.8 Automatic placement and routing   |          | 68             |

|   | 4.3 | Architecture Features                   |          | 69             |

|   | 4.4 | Validation                              |          | 71             |

|   |     | 4.4.1 Software flow                     |          | 71             |

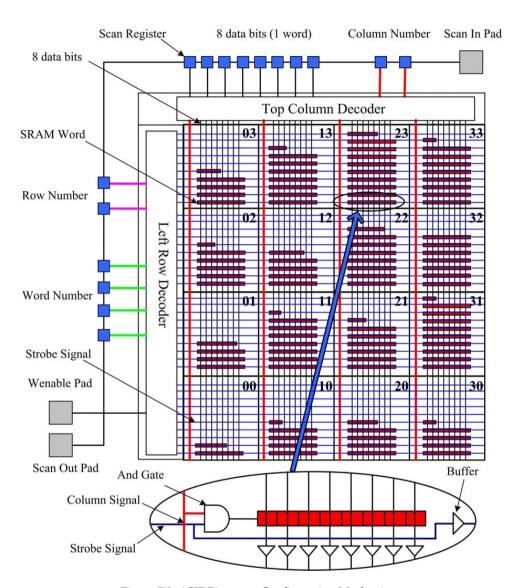

|   |     | 4.4.2 Bitstream configuration mechanism |          | 71             |

|   |     | 4.4.3 Simulation                        |          | 72             |

|   |     | 4.4.4 Netlist layout comparison         |          | 73             |

|   |     | 4.4.5 Electric Simulation               |          | 73             |

|   | 4.5 | Tapeout                                 |          | 74             |

|   | 4.6 | Conclusion and Future Work              |          | 74             |

| 5 | ASI | F: Application Specific Inflexible FPGA |          | 77             |

|   | 5.1 | Introduction and Previous Work          |          | 77             |

|   | 5.2 | Reference FPGA architecture             |          | <del>7</del> 9 |

|   | 5.3 | ASIF Generation Techniques              |          | 80             |

|   |     | 5.3.1 ASIF-1 (No wire sharing)          |          | 82             |

|   |     | 5.3.2 ASIF-2 (Wire sharing)             |          | 82             |

|   |     | 5.3.3 ASIF-3 (Efficient wire sharing)   |          | 82             |

|   |     | 5.3.4 ASIF-4 (Efficient placement)      |          | 85             |

|   | 5.4 | ASIF Exploration Environment            |          | 87             |

|   | 5.5 | Area Model                              |          | 88             |

|   | 5.6 | Experimentation and Analysis            |          | 90             |

|   |     | 5.6.1 MCNC benchmark circuits           |          | 90             |

|   |     | 5.6.2 Results and Analysis              |          | 90             |

|   |     | 5.6.3 Effect of LUT size on ASIF        |          | 95             |

|   | 5.7 | Quality Analysis                        |          | 95             |

|   | 5.8 | Conclusion                              |          | 100            |

| 6 | ASI | F using Heterogeneous Logic Blocks      |          | 103            |

|   | 6.1 | ASIF Generation Technique               |          | 104            |

|   | 6.2 | Experimentation and Analysis            |          | 105            |

|   |     | 6.2.1 Opencores benchmark circuits      |          | 105            |

|   |     | 6.2.2 Results and Analysis              |          | 105            |

|   | 6.3 | Mapping application circuits on ASIF    |          | 112            |

| • • |          |

|-----|----------|

| X11 | Contents |

|     |          |

|    |       | 6.3.1  | Introduction                                       | 112 |

|----|-------|--------|----------------------------------------------------|-----|

|    |       | 6.3.2  | Algorithm                                          | 112 |

|    |       | 6.3.3  | Results and Analysis                               | 116 |

|    | 6.4   | Concl  | usion and Future Work                              | 117 |

|    |       |        |                                                    |     |

| 7  | ASI   |        | ware Generation                                    | 119 |

|    | 7.1   | Introd | uction and Previous Work                           | 119 |

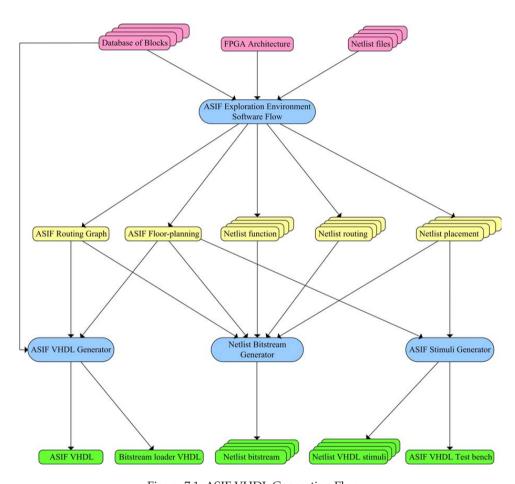

|    | 7.2   | ASIF ( | Generation                                         | 122 |

|    |       | 7.2.1  | ASIF Generation Flow                               | 122 |

|    |       | 7.2.2  | Example Architecture                               | 122 |

|    |       | 7.2.3  | ASIF Configuration Mechanism                       | 124 |

|    |       | 7.2.4  | ASIF VHDL Generation                               | 126 |

|    |       | 7.2.5  | Loader VHDL Generation                             | 128 |

|    |       | 7.2.6  | Netlist Bitstream Generation                       | 129 |

|    |       | 7.2.7  | Stimuli Generation                                 | 130 |

|    | 7.3   | Valida | tion                                               | 131 |

|    | 7.4   | ASIF 1 | Layout Generation                                  | 132 |

|    | 7.5   | Exper  | iments and Analysis                                | 133 |

|    |       | 7.5.1  | Opencores circuits                                 | 133 |

|    |       | 7.5.2  | Results and Analysis                               | 133 |

|    | 7.6   | Concl  | usion and Future Work                              | 135 |

|    |       |        |                                                    |     |

| 8  | Con   |        | and Future Lines of Research                       | 139 |

|    | 8.1   | Summ   | nary of contributions                              | 139 |

|    |       | 8.1.1  | Heterogeneous architecture exploration environment | 139 |

|    |       | 8.1.2  | Tile-based layout generator for FPGAs              | 140 |

|    |       | 8.1.3  | ASIF : Application Specific Inflexible FPGA        | 140 |

|    |       | 8.1.4  | ASIF Hardware Generation                           | 141 |

|    | 8.2   | Future | e work                                             | 142 |

| Bi | bliog | raphy  |                                                    | 145 |

|    |       |        |                                                    |     |

# List of Figures

| 1.1  | Comparison of different platforms used for implementing digital applications       | 2  |

|------|------------------------------------------------------------------------------------|----|

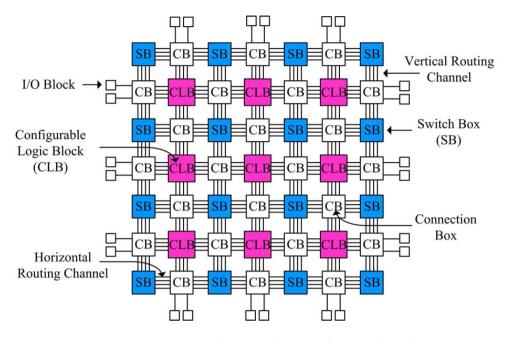

| 2.1  | Overview of FPGA Architecture [Betz et al., 1999]                                  | 10 |

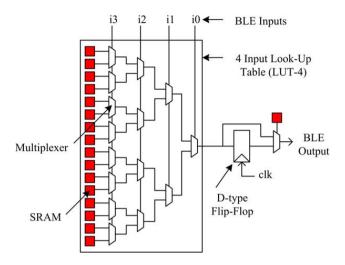

| 2.2  | Basic Logic Element (BLE)                                                          | 11 |

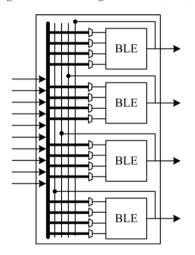

| 2.3  | A Configurable Logic Block (CLB) having four BLEs                                  | 11 |

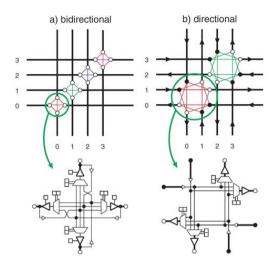

| 2.4  | Switch Block, length 1 wires [G.Lemieux et al., 2004]                              | 12 |

| 2.5  | Channel segment distribution                                                       | 13 |

| 2.6  | FPGA software configuration flow                                                   | 14 |

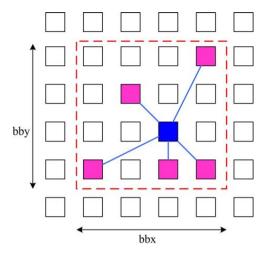

| 2.7  | Bounding box of a hypothetical 6-terminal net [Betz et al., 1999]                  | 15 |

| 2.8  | Modeling FPGA architecture as a directed graph [Betz et al., 1999]                 | 16 |

| 2.9  | A Heterogeneous FPGA in VPR 5.0 [Luu et al., 2009]                                 | 20 |

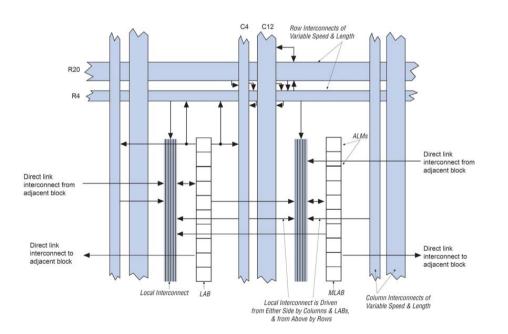

| 2.10 | Stratix IV architectural elements                                                  | 21 |

| 2.11 | Stratix IV LAB Structure                                                           | 22 |

| 2.12 | $FPGA/Structured-ASIC\ (HardCopy)\ Correspondence\ [Hutton\ et\ al.,\ 2006]\ .\ .$ | 23 |

| 2.13 | A VLIW Processor Architecture with Application Specific Hardware Func-             |    |

|      | tions [Jones et al., 2005]                                                         | 25 |

|      | A Reconfigurable Arithmetic Array for Multimedia Applications                      | 26 |

| 2.15 | A basic cell of RaPiD [Ebeling et al., 1996]                                       | 27 |

| 2.16 | Comparison of different solutions used to reduce ASIC and FPGA drawbacks           | 29 |

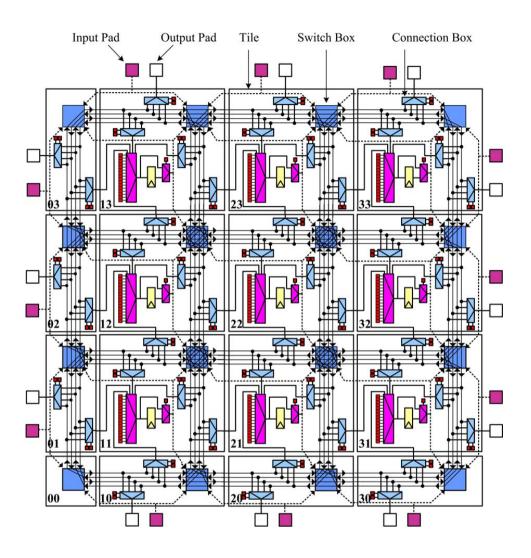

| 3.1  | Heterogeneous FPGA with bidirectional routing network                              | 33 |

| 3.2  | A single CLB block with unidirectional routing network                             | 34 |

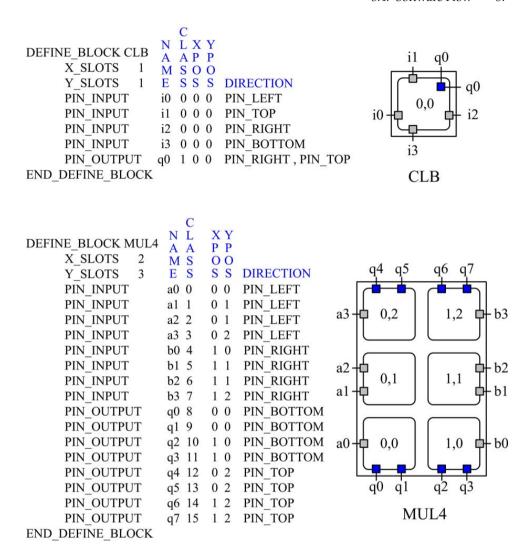

| 3.3  | CLB and MUL4 Block definition example                                              | 37 |

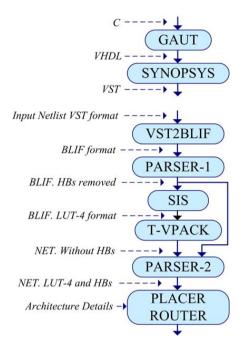

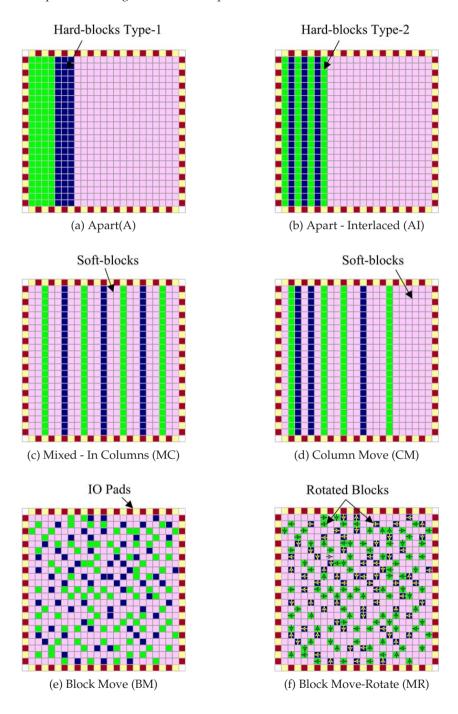

| 3.4  | Software Flow                                                                      | 38 |

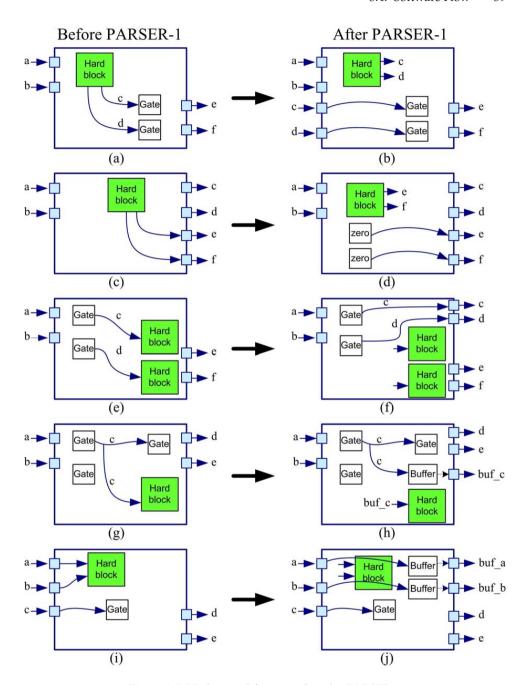

| 3.5  | Netlist modifications done by PARSER-1                                             | 39 |

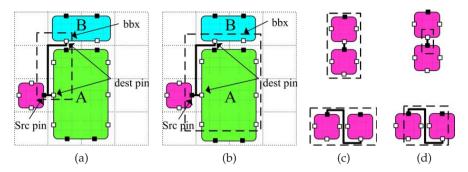

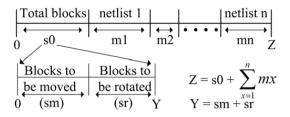

| 3.6  | Bounding Box                                                                       | 40 |

| 3.7  | Source Selection                                                                   | 42 |

| 3.8  | Block Movement                                                                     | 44 |

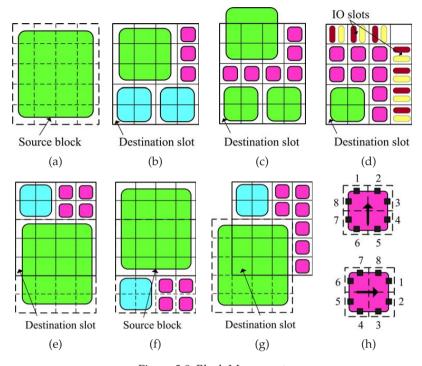

| 3.9  | Different Floor-Plannings                                                          | 46 |

|      | Experimental Flow                                                                  | 48 |

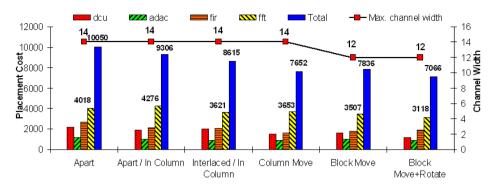

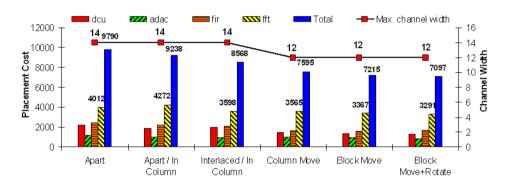

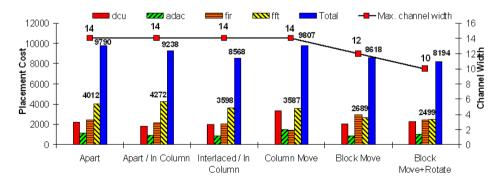

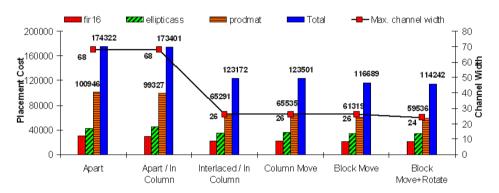

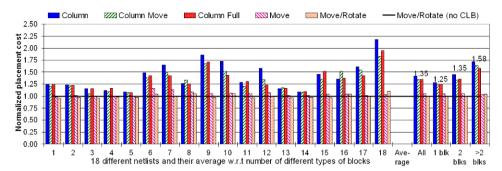

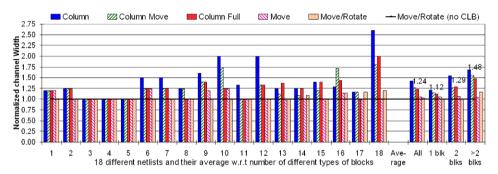

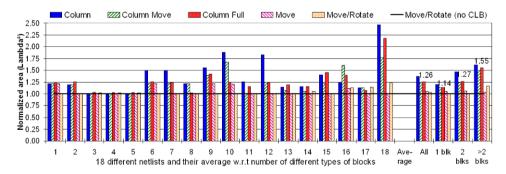

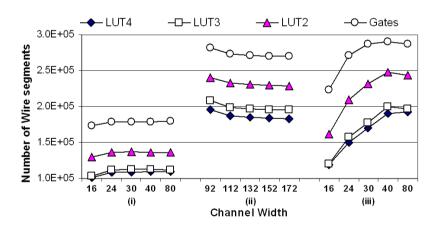

|      | Experimental results for Netlist-1 (Stratus) using common architecture             | 53 |

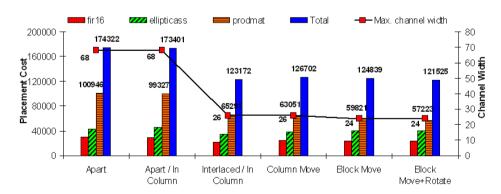

|      | Experimental results for Netlist-2 (GAUT) using common architecture                | 54 |

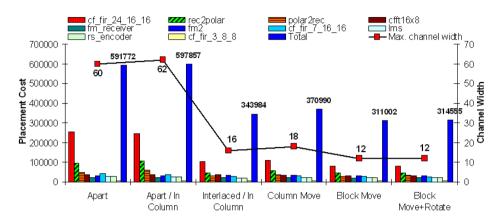

|      | Experimental results for Netlist-3 (Opencores) using common architecture           | 55 |

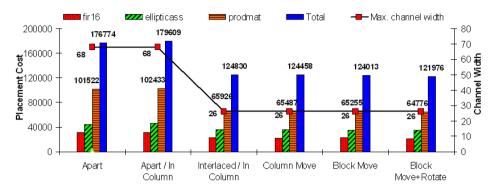

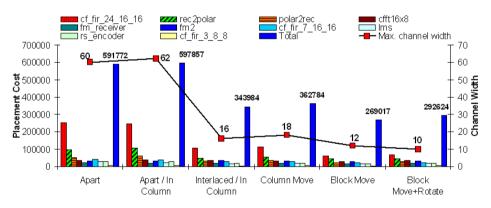

|      | Experimental results for Netlist-3                                                 | 58 |

#### xiv List of Figures

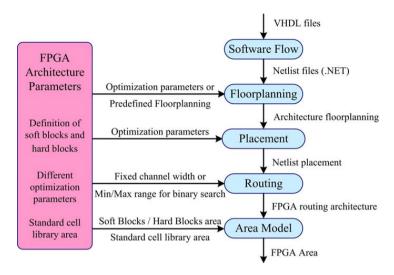

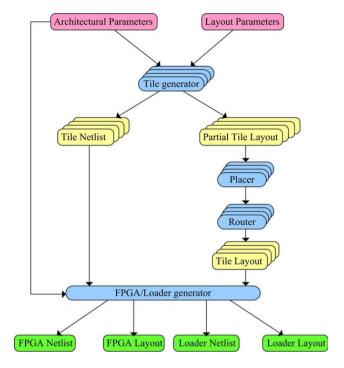

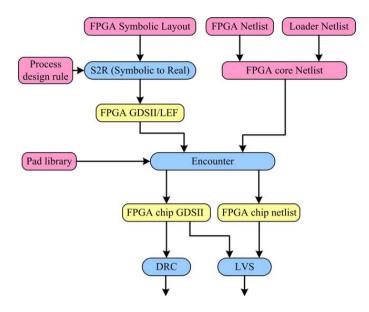

| 4.1  | Complete FPGA generation CAD flow                                                  | 63  |

|------|------------------------------------------------------------------------------------|-----|

| 4.2  | Tiles for Mesh-based FPGA                                                          | 64  |

| 4.3  | Partial layout of a sample FPGA Tile                                               | 65  |

| 4.4  | H-Tree clock distribution network for 8x8 FPGA                                     | 66  |

| 4.5  | Tiles for construction a H-Tree clock distribution Network                         | 67  |

| 4.6  | Symbolic layout generation of an FPGA Tile                                         | 69  |

| 4.7  | Error detection method to mitigate single event upset                              | 70  |

| 4.8  | Software Flow                                                                      | 71  |

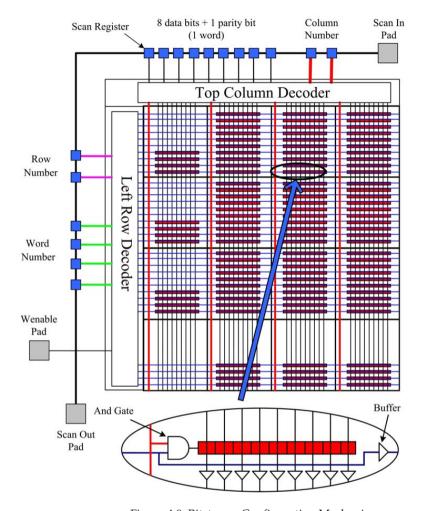

| 4.9  | Bitstream Configuration Mechanism                                                  | 72  |

| 4.10 | CAD flow for FPGA chip generation, verification and validation                     | 73  |

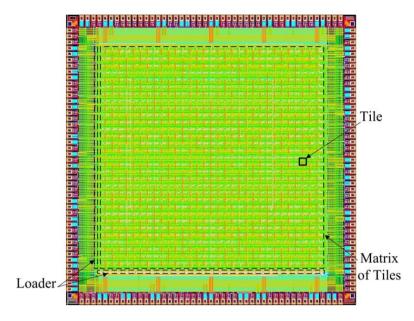

| 4.11 | A Prototype 32x32 FPGA Chip Layout using 130 nm process                            | 75  |

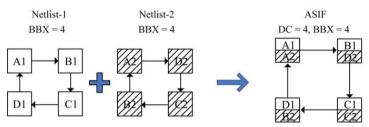

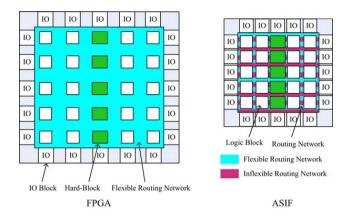

| 5.1  | An illustration of ASIF generation concept                                         | 78  |

| 5.2  | Example Circuits                                                                   | 80  |

| 5.3  | Example circuits mapped on FPGA                                                    | 81  |

| 5.4  | Efficient Wire Sharing                                                             | 83  |

| 5.5  | Efficient Placement                                                                | 86  |

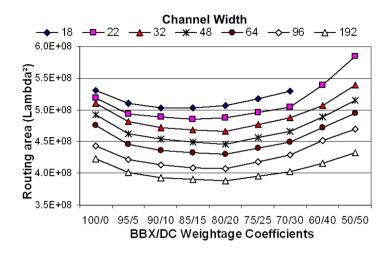

| 5.6  | ASIF-4 for 17 netlists with varying channel widths, weightage coefficients $$ . $$ | 91  |

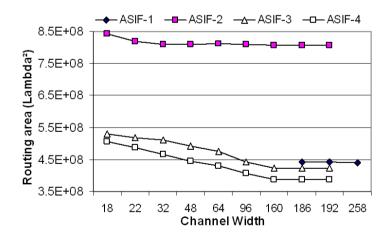

| 5.7  | Routing area comparison for different ASIFs for 17 netlists                        | 91  |

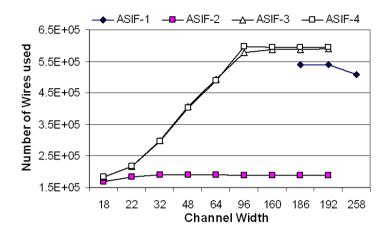

| 5.8  | Wire count comparison for different ASIFs for 17 netlists                          | 93  |

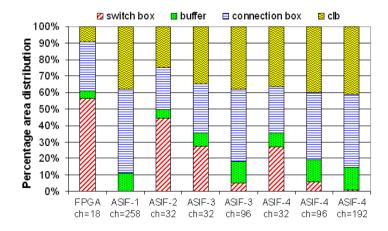

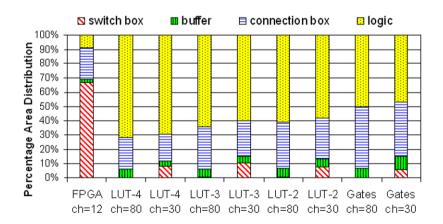

| 5.9  | Percentage area distribution for FPGAs and ASIFs                                   | 93  |

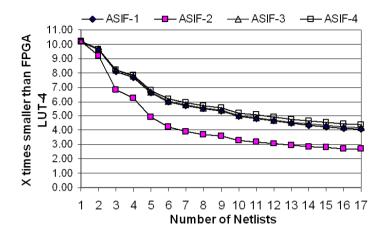

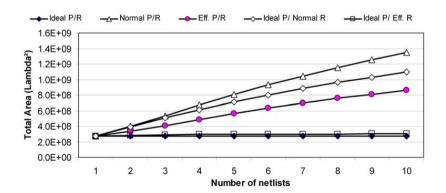

|      | FPGA vs. ASIFs with varying number of netlists                                     | 94  |

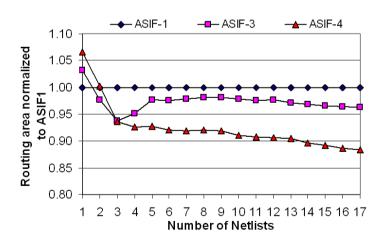

|      | Comparison of different ASIFs normalized to ASIF-1                                 | 94  |

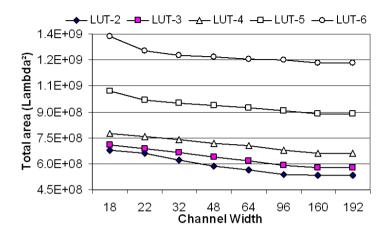

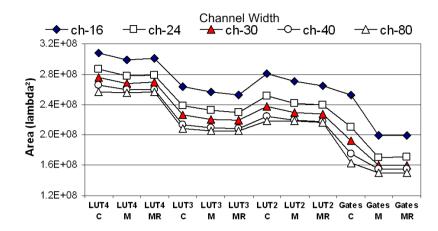

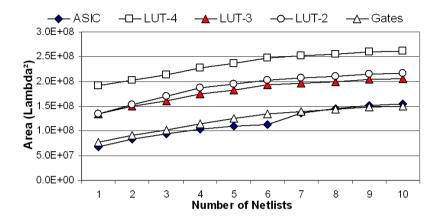

|      | Area comparison for ASIF-4 of 17 netlists with varying LUT sizes                   | 96  |

|      | Wire count comparison for ASIF-4 of 17 netlists with varying LUT sizes             | 96  |

|      | FPGA vs. ASIF-4 with varying LUT sizes and number of netlists                      | 97  |

|      | Percentage area distribution for FPGAs and ASIF-4 with varying LUT sizes .         | 97  |

|      | ASIF quality measurement for 10 tseng netlists                                     | 99  |

| 5.17 | ASIF quality measurement for 10 pdc netlists                                       | 99  |

| 6.1  | An FPGA and an ASIF using Heterogeneous logic blocks                               | 104 |

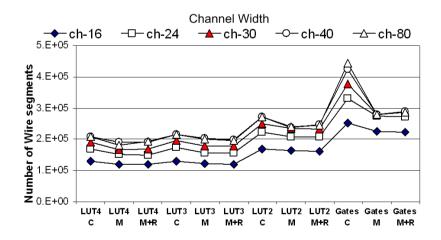

| 6.2  | Area comparison of ASIFs with different netlists/floor-plannings                   | 108 |

| 6.3  | Wire count comparison for different ASIFs                                          | 108 |

| 6.4  | Area comparison for ASIFs with different Placement/Routing                         | 109 |

| 6.5  | Wire count comparison for ASIF with different Placement/Routing                    | 109 |

| 6.6  | ASIC vs. ASIFs with varying LUT sizes and number of netlists                       | 111 |

| 6.7  | Percentage area distribution for FPGAs and ASIFs                                   | 111 |

| 6.8  | Can an application be mapped on an ASIF?                                           | 112 |

| 6.9  | Algorithm to place netlist on ASIF                                                 | 115 |

| 7.1  | ASIF VHDL Generation Flow                                                          | 121 |

| 7.2  | A 3x3 FPGA with single-driver, unidirectional routing network $\dots \dots$        | 123 |

| 7.3  | ASIF Bitstream Configuration Mechanism                                             | 125 |

| 7.4  | ASIF VHDL generation from routing graph                                            | 127 |

| 7.5 | Four input Look-Up Table configuration for different pin connectivity        | 131 |

|-----|------------------------------------------------------------------------------|-----|

| 7.6 | Algorithm to change LUT configuration for different pin connectivity order . | 132 |

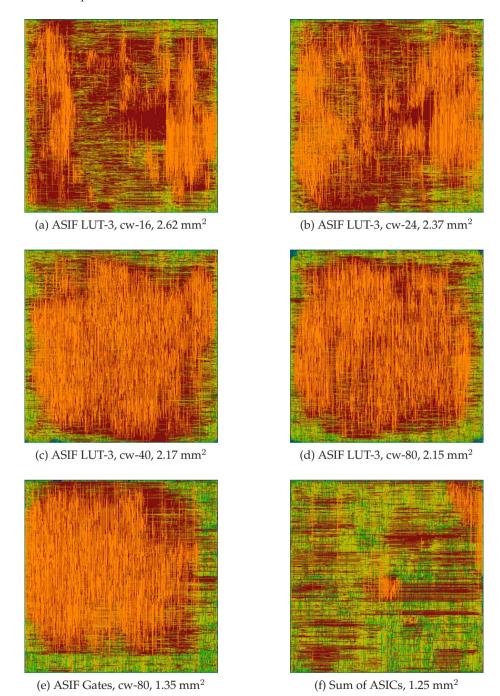

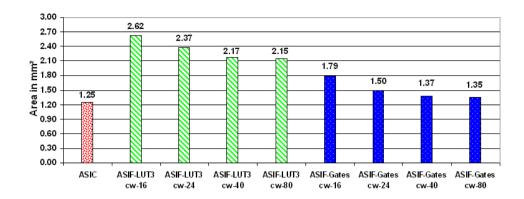

| 7.7 | ASIC/ASIF layout for 10 opencores circuits using 130nm process of ST         | 134 |

| 7.8 | ASIC vs ASIF for 10 opencores circuits using 130nm ST standard cell library  | 136 |

| 7.9 | Percentage SRAM area in ASIFs (Layout done with LATCH instead of SRAM)       | 136 |

|     |                                                                              |     |

| 8.1 | An illustration of ASIF blocks integrated in an FPGA                         | 142 |

List of Figures

xv

## List of Tables

| 3.1 | Architecture Description File Parameters               | 35  |

|-----|--------------------------------------------------------|-----|

| 3.2 | Block definition                                       | 35  |

| 3.3 | Standard cells area                                    | 47  |

| 3.4 | Netlist-1 block utilization table - Stratus Netlists   | 50  |

| 3.5 | Netlist-2 block utilization table - GAUT Netlists      | 50  |

| 3.6 | Netlist-3 block utilization table - Opencores Netlists | 50  |

| 3.7 | Netlist-4 block utilization table                      | 57  |

| 5.1 | MCNC benchmark circuits                                | 89  |

| 6.1 | Netlist Version-lut4,-lut3,-lut2                       | 106 |

| 6.2 | Netlist Version-Gates                                  | 106 |

| 6.3 | Placement Execution Time (in seconds)                  | 116 |

# Introduction

1

#### 1.1 Background

Field Programmable Gate Arrays (FPGAs) are reconfigurable devices that can execute variety of hardware applications. A software CAD flow transforms a hardware application to a programming bitstream, which can easily be and instantly programmed on an FPGA. This re-programmability of an FPGA device can be used to execute different hardware applications at mutually exclusive times. Similarly any errors or updates in the final product can be corrected/upgraded by simply reprogramming the FPGA. An FPGA also allows partial re-configuration i.e, only a portion of an FPGA is configured while other portions are still running. Partial re-configuration is useful in designing systems which require to adapt frequently according to run-time constraints. Compared to alternate technologies that fabricate specific application circuits on silicon, FPGA-based applications have less non recurring engineering (NRE) cost and shorter time-to-market. These advantages make FPGA-based products very effective and economical for low to medium volume production.

The flexibility and reusability of an FPGA is due to its configurable logic blocks that are interconnected through configurable routing resources. An application design can easily be mapped on these configurable resources of an FPGA by using a dedicated software flow. This application is initially synthesized into interconnected logic blocks (generally comprising of Look-Up Tables and Flip-Flops). The logic block instances of the synthesized circuit are then placed on configurable logic blocks of FPGA. The placement is done in such a way that minimum routing resources are required to interconnect them. Connections between these logic blocks are later routed using configurable routing resources. The logic blocks and routing resources are programmed by static RAMs (SRAMs) which are distributed through

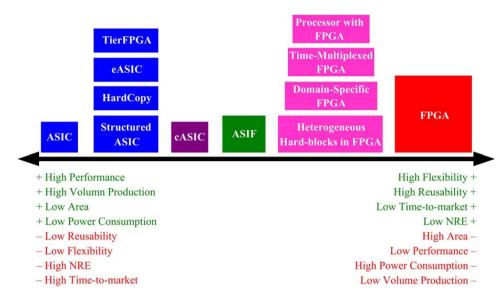

Figure 1.1: Comparison of different platforms used for implementing digital applications

out the FPGA. Once an application circuit is placed and routed on the FPGA, the SRAM bit information of the entire FPGA is gathered to form a bitstream. This bitstream is then programmed on the SRAMs of FPGA by a bitstream loader, which is integrated in the FPGA. This work focuses only on SRAM-based FPGA devices, as they are the most commonly used commercial FPGAs. Other technologies used to implement configuration memory includes antifuses [J.Greene et al., 1993] and floating gate transistors [S.Brown, 1994].

An FPGA device can be compared to other digital computational devices. The section below presents a broad overview and their comparison with FPGAs.

#### 1.1.1 Microprocessors

A microprocessor is a general purpose hardware device that can execute a software task. The software task is represented as a stream of software instructions; each instruction belongs to a pre-defined instruction-set. The instructions in a task are executed on the microprocessor in a serial manner. These instructions are stored in instruction memory, whereas data to be processed is stored in data memory or general purpose registers. Each instruction is executed as a set of machine operations, which generally comprise of (i) Instruction Fetch (IF): A software instruction is fetched from memory. (ii) Instruction Decode(ID): Instruction is decoded, and registers are accessed from the register file. (iii) Execute (EX): Instruction is executed according to its type. The execution may include an ALU operation on operands (registers and/or immediate values). (iv) Memory Access (MEM): Loads data from memory to register, or stores data from register to memory. (v) Write back (WB): Computed result is written back to register. If each machine operation takes one machine cycle, then one software instruction will take 5 machine cycles to execute. However, pipelining technique can be employed by starting a new instruction on each machine cycle. In this way multiple software instructions are overlapped in execution.

An FPGA can be compared to a microprocessor, as both are flexible and reprogrammable. However, the configurability of FPGAs is fundamentally different from the programmability of a traditional microprocessor. A microprocessor can execute software applications, whereas an FPGA can execute hardware applications. The functional logic blocks in a traditional microprocessor cannot be configured for different software programs. Whereas logic

blocks in an FPGA can be configured differently for each application. The limited number of non-reconfigurable functional units in a microprocessor are carefully selected by the microprocessor architect in accordance with the generic software needs. These functional units and their intercommunication is optimized to achieve very high clock frequencies. A microprocessor takes varying number of clock cycles to execute different software instructions.

Execution of a hardware application design enjoys inherent parallelism. On the contrary, a stream of software instructions are executed sequentially on a microprocessor. Hardware implementation can use any required hardware functionality to execute a particular task. Whereas a software implementation might require several software instructions to execute the same task. Due to these reasons, hardware implementation of a particular design is generally much faster than its software implementation. Although, due to internal architecture, the clock frequencies of FPGAs are very low as compared to that of microprocessors. Nevertheless, a task running on an FPGA is generally much faster than the same task running on a microprocessor.

#### 1.1.2 Application-specific instruction-set processor (ASIPs)

An application-specific instruction-set processor (ASIP) is designed according to requirements of a particular application. The instruction-set of an ASIP is specifically designed to accelerate most commonly used complex functions required by the particular application domain. A general purpose microprocessor is generally designed to achieve maximum performance with maximum flexibility. Whereas, an ASIP reduces the flexibility to achieve better performance gains for a pre-defined application domain. ASIP examples includes DSP, media, network and other domain-specific processors.

#### 1.1.3 Application Specific Integrated Circuits (ASICs)

An ASIC is a digital device that is customized to perform a particular task. The functionality of an ASIC is defined by using a hardware description language (HDL) such as Verilog or VHDL. After the functional verification of HDL, it is synthesized into a netlist of low-level gates called as standard-cells. The standard-cells are taken from a pre-characterized standard-cell library which comprise of gates such as 2 input and, 2 input nor etc. After the synthesis, a placement tool places the standard cells on a region representing the ASIC. The standard cells are placed in accordance to a variety of placement constraints. After the placement, routing tool uses the placement information and connects electrical connections between the standard cells. The final output is used to fabricate a physical IC of the ASIC. The standard-cell library can be used along with modern CAD systems can offer considerable performance/cost benefits. Instead of using standard-cell library, the layout can be designed in full-custom by laying out each individual transistor and their interconnection. Full-custom design improves the area and performance of the ASIC, however it is an extremely labor-intensive task, and requires higher skills. It increases the design time, increases non-recurring engineering (NRE) cost, and the time-to-market of the product.

#### 4 Chapter 1. Introduction

When an FPGA is compared to an ASIC, it is revealed that all the advantages of an FPGA come with a very huge cost. A circuit implemented on an FPGA is generally 35 times larger, 4 times slower, and 14 times more power consuming than the same circuit implemented in a standard-cell based ASIC [I.Kuon and J.Rose, 2007]. Consequently, FPGAs are unsuitable for applications requiring high volume production, high performance or low power consumption. However, ASICs suffer from inflexibility, higher non-recurring engineering (NRE) cost and higher time-to-market. Thus, ASICs are only suitable if produced in high volumes. Moreover, any corrections or updates in an ASIC based product requires a re-spin, which further increases time-to-market.

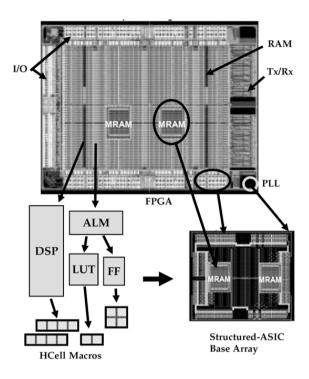

#### 1.1.4 Structured-ASICs

The NRE cost and time-to-market of an ASIC are reduced with the advent of a new breed of ASICs know as Structured-ASICs. Structured-ASICs consist of an array of optimized logic elements on lower mask layers. A desired functionality is implemented on it by making changes on few upper mask layers. The upper mask layers are used to customize connections between pre-defined logic elements on lower mask layers. Compared to cell-based ASICs, the design and manufacturing time is reduced in structured-ASIC due to its predefined metal layers. The power and clock distribution networks are predefined in structured-ASICs. The CAD tools generally cost lower and are easier to use than the cell-based ASIC tools.

Structured-ASICs are explored or manufactured by several companies [Wu and Tsai, 2004] [Okamoto et al., 2004] [Sherlekar, 2004] [eASIC, 2010]. FPGA vendors have also started giving provision to migrate FPGA based application to Structured-ASIC. The main idea is to prototype, test and even ship initial few designs on an FPGA; later it can be migrated to Structured-ASIC for high volume production [Hutton et al., 2006]. In this regard, Altera has proposed a clean migration methodology [Pistorius et al., 2007] that ensures equivalence verification between FPGA and its Structured-ASIC (known as HardCopy [HardCopy, IV]). However, migration of an FPGA based product to a Structured-ASIC supports only a single application design. HardCopy totally loses the quality of an FPGA to use the same hardware for executing multiple applications at different times. An Application Specific Inflexible FPGA (ASIF) proposed in this work retains this property and can be a possible future extension for HardCopy. Figure 1.1 presents a rough comparison of different platforms that can be used for implementing digital applications.

#### 1.2 Motivation and contribution

The global theme of this work is to reduce the drawbacks of an FPGA when compared to an ASIC i.e, to make it viable for applications requiring high volume production, high performance or low power consumption. The main focus of this work is to reduce the area of an FPGA. Speed and power are not directly taken into consideration. Reduced area generally

tend to give improvement in speed and power. Area of an FPGA is improved by employing two broad techniques

- Logic flexibility of an FPGA is reduced by inserting heterogeneous hard-blocks, such as multipliers, adders etc.

- Routing flexibility of an FPGA is reduced by proposing ASIF (Application Specific Inflexible FPGA)

Considerable amount of logic and routing resources can be saved if a particular hard-block is directly embedded into an FPGA. The types and quantities of hard-blocks in an FPGA can be decided from the application domain for which an FPGA is required. Similarly, the area of an FPGA can be decreased by reducing the routing network of an FPGA for a given set of application circuits. Such a reduced FPGA is called as an Application Specific Inflexible FPGA (ASIF). An ASIF can be used under two main scenarios. (i) A product is designed and tested on an FPGA. It can be migrated to an ASIF for high volume production. (ii) ASIF generation techniques can be used to generate a configurable ASIC core that can perform multiple tasks at different times.

The major contribution of this book includes the following:

#### 1.2.1 Exploration environment for heterogeneous FPGA Architectures

A new software environment is proposed for the exploration of heterogeneous FPGA architectures. An architecture description mechanism is used to select different FPGA architectural parameters. New heterogeneous blocks can also be easily defined. A software CAD flow is used to map an application circuit on the newly defined FPGA architecture. The software flow not only maps the instances of a target netlist on their respective blocks in the architecture, but also refines the floor-planning of heterogeneous blocks on the architecture. This environment is used to define and optimize FPGA architectures for a particular application domain. Heterogeneous FPGA architectures are generated for a set of different benchmark circuits. Different automatic and manual floor-planning techniques are used to show the effect of floor-planning on the overall area of heterogeneous FPGAs.

The novelty of the proposed exploration environment is its ability to optimize the floorplanning of heterogeneous blocks on the FPGA architecture. The floor-planning can be optimized for a given set of application circuits. Existing exploration environments propose a pre-determined floor-planning organization. They do not consider the problem of optimizing the floor-planning automatically.

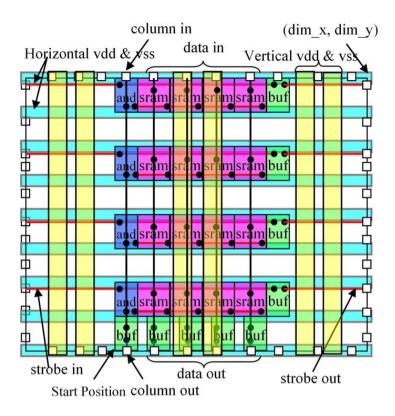

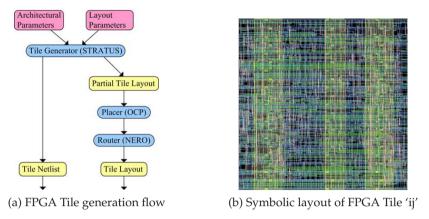

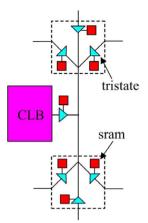

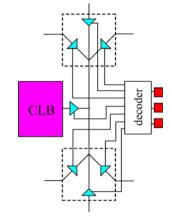

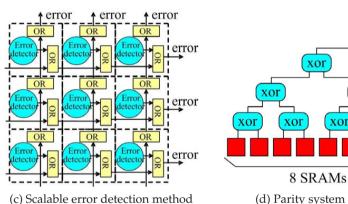

#### 1.2.2 Automatic FPGA layout generation

An automated method is proposed for the generation of FPGA layout. The main purpose of developing a layout generator is to reduce the overall FPGA design time with limited area

penalty. This generator works in two phases. In the first phase, a partial layout is generated using generic parameterized algorithms. The partial layout is generated to obtain a fast bit-stream configuration mechanism, an optimized power routing and a balanced clock distribution network. In the second phase, the generator completes the remaining layout using automatic placer and router. This two-phase technique allows better maneuvering of the layout according to desired constraints. FPGA layout is generated using a symbolic standard-cell library which allows to migrate the symbolic layout to any fabrication process technology. The proposed method is validated by generating layout of a 1024 Look-Up Table based mesh FPGA architecture. The layout is successfully taped-out using 130nm 6-metal layer CMOS process of STMicroelectronics [STMicroelectronics, 2010].

Previously proposed FPGA layout generators use commercial VLSI tools. The proposed tile-based FPGA layout generator uses open-source VLSI tools, which can be adapted for possible future demands. Another major contribution is the concept of manual intervention in automatic layout generation. Manual intervention in layout generation, attained through generic layout parameters, allows to maneuver the layout according to desired constraints.

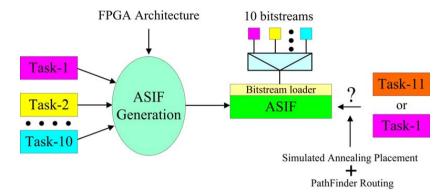

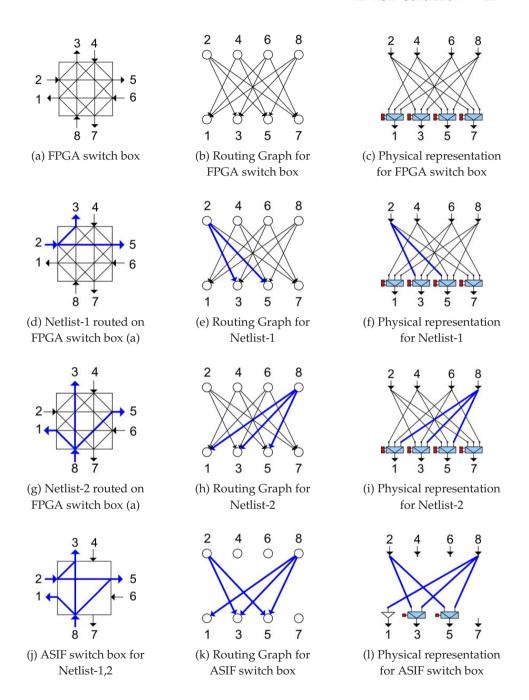

#### 1.2.3 ASIF: Application Specific Inflexible FPGA

An Application Specific Inflexible FPGA (ASIF) is an FPGA with reduced flexibility that can implement a set of application circuits which will operate at mutually exclusive times. These circuits are efficiently placed and routed on an FPGA to minimize total routing switches required by the architecture. Later, all unused routing switches are removed from the FPGA to generate an ASIF. An ASIF for a set of 20 MCNC benchmark circuits is found to be 82% smaller than a mesh-based unidirectional FPGA required to map any of these circuits. An ASIF for a set of circuits is also compared with the sum of areas of standard-cell based ASICs of given circuits. An ASIF can also be reprogrammed to execute new or modified circuits, but unlike FPGAs, at a limited scale. A new CAD flow is proposed which can map application circuits on an ASIF.

A novel concept of application specific inflexible FPGA (ASIF) is proposed. Existing placement and routing algorithms are modified to propose efficient placement and routing techniques. Efficient placement and routing techniques are used to minimize the area of an ASIF. The concept of ASIF is also applied on heterogeneous FPGA architectures, thus proposing heterogeneous-ASIF. A new branch-and-bound based placement algorithm is proposed to map new application circuits on an ASIF.

#### 1.2.4 Automatic ASIF hardware generation

An automated method of generating ASIF hardware is proposed. The ASIF VHDL generator is integrated with the ASIF exploration environment. By doing so, all the ASIF architectural parameters supported by the exploration environment can be automatically translated to a

synthesizable VHDL netlist. The synthesized VHDL model of the ASIF is later passed to Cadence Encounter [Cadence, 2010] to generate its layout. The layout of ASIF is generated with a different technique than the automatic tile-based FPGA layout generator referred to earlier. The tile-based FPGA layout generator has its own advantages. However, one of its main disadvantages is that it is not directly linked to the architecture exploration environment. Any changes done in the architecture exploration environment are not immediately reflected in the layout generator. Since, ASIF is still in the process of exploration, we preferred to generate the VHDL of an ASIF by using different data-structures of ASIF exploration environment. The exploration environment also generates programming bitstream for each netlist used in the generation of on ASIF. The VHDL model of the generated ASIF is simulated using Synopsys [Synopsys, 2010]; bitstreams of different application circuits are individually programmed on the ASIF to execute different application circuits exclusively. The VHDL model of the ASIF is later passed to Cadence Encounter to generate layout of ASIF using 130nm 6-metal layer CMOS process of STMicroelectronics [STMicroelectronics, 2010].

#### 1.3 Field of Applications

ASIF generation techniques can be employed for any digital product that provides multiple functionalities at exclusive times. Such a digital product may comprise of a video application, a multi-standard radio application, or any set of DSP functionalities required at different times. Suppose, a hardware circuit is required for executing various digital algorithms required for a camera. The lens of a camera sends RGB frames to the display screen of camera. The received RGB frames can also be encoded as a video or an image using their respective encoders. After the video or an image is recorded, they can be viewed on the camera screen using their respective decoders. Different quality requirements may require the camera to use different video compression techniques, such as H.264 and MPEG-4. Similarly different image compression techniques may also be used, such as JPEG and PNG. Such camera requires a set of 8 different digital circuits at exclusive times, i.e. encoder/decoder pairs for H.264, MPEG-4, JPEG and PNG. Each time a particular functionality is required, a control circuitry programs the bitstream of the desired function on FPGA. These eight digital circuits can be designed and tested on an FPGA. Later, for high volume production, the FPGA can be reduced to an ASIF for the given eight application circuits. Similarly, an ASIF can also be used after an RF ADC [Beilleau et al., 2009].

#### 1.4 Book Organization

This dissertation is organized as follows. Chapter 2 presents the state-of-the-art of FPGA architectures and CAD tools. It also presents new architectures that are proposed to resolve different drawbacks of FPGAs. Chapter 3 presents an environment for the exploration of mesh-based heterogeneous FPGA architectures. Chapter 4 presents an automated method for the generation of a tile-based FPGA layout. Chapter 5 describes different ASIF generation

#### 8 Chapter 1. Introduction

techniques and their comparison with FPGAs. Chapter 6 presents ASIFs using heterogenous logic blocks, and their comparison with the sum of areas of standard-cell based ASICs of given circuits. It also presents a CAD flow to map new or modified application circuits on an ASIF. Chapter 7 presents automatic hardware generation of ASIFs, and their layout generation using Cadence Encounter. Finally Chapter 8 presents a conclusion and future work.

2

#### State of the art

#### 2.1 Introduction to FPGAs

A Field programmable Gate Array (FPGA) is an integrated circuit that is designed to be configured after manufacturing. FPGAs can be used to implement any logic function that an Application Specific Integrated Circuit (ASIC) can perform. For varying requirements, a portion of FPGA can also be partially reconfigured while the rest of an FPGA is still running. Unlike other technologies, which implement hardware directly into silicon, any errors in the final FPGA-based product can be easily corrected by simply reprogramming the FPGA. Any future updates in the final product can also be easily upgraded by simply downloading a new application bitstream. The ease of programming and debugging with FPGAs decreases the overall non-recurring-engineering (NRE) costs and time-to-market of FPGA-based products.

The reconfigurability of FPGAs is due to their reconfigurable components called as logic blocks, which are interconnected by a reconfigurable routing network. There are two main routing interconnect topologies: Tree-based routing network [A.DeHon, 1999] [Marrakchi et al., 2009] and Mesh-based routing network [Betz et al., 1999]. A tree-based FPGA architecture is created by connecting logic blocks into clusters. These clusters are connected recursively to form a hierarchical structure. On contrary, a mesh-based FPGA architecture interconnects logic blocks through a 2-D mesh of routing network. Tree-based interconnect topology occupies less area than the mesh-based interconnect topology [Marrakchi, 2008], however a tree-based FPGA suffers from layout scalability problems. The layout of a mesh-based FPGA is scalable and is thus commonly used by commercial FPGA vendors such as Xilinx [Xilinx, 2010] and Altera [Altera, 2010]. This work focuses only on mesh-based routing

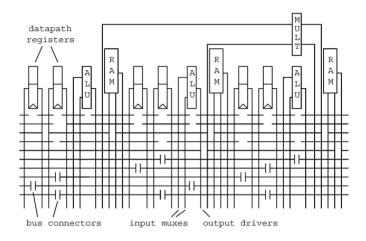

Figure 2.1: Overview of FPGA Architecture [Betz et al., 1999]

#### topology.

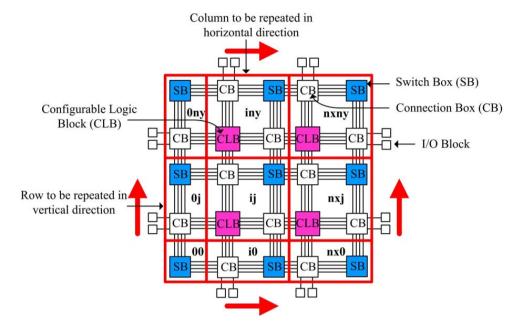

Figure 2.1 shows a traditional mesh-based FPGA architecture. The configurable logic blocks (CLBs) are arranged on a 2D grid and are interconnected by a programmable routing network. The Input/Output (I/O) blocks on the periphery of FPGA chip are also connected to the programmable routing network. The routing network comprises of horizontal and vertical routing channel tracks. Switch boxes connect horizontal and vertical routing tracks of the routing network. Connection boxes connect logic and I/O block pins with adjacent routing tracks. A software flow converts a target hardware circuit into interconnected CLBs and I/O instances, and then maps them on the FPGA. The software flow also generates a bitstream, which is programmed on the FPGA to execute the target hardware circuit. The mesh-based FPGA, and its software flow is described in detail as below.

#### 2.1.1 Configurable Logic Block

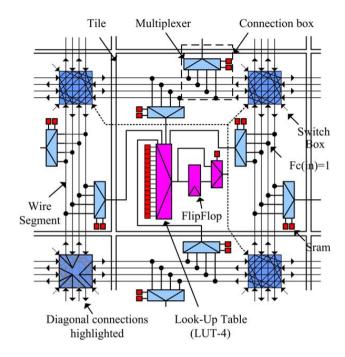

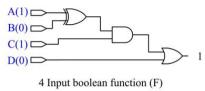

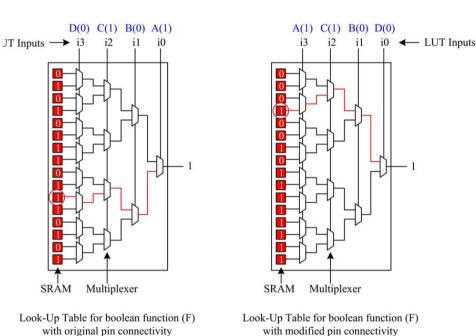

A configurable logic block (CLB) is a basic component of an FPGA that implements logic functionality of a target application design. A CLB can comprise of a single basic logic element (BLE), or a cluster of locally interconnected BLEs. A simple BLE consists of a Look-Up Table (LUT), and a Flip-Flop. A LUT with k inputs (LUT-k) contains  $2^k$  configuration bits; it can implement any k-input boolean function. Figure 2.2 shows a simple BLE comprising of a 4 input Look-Up Table (LUT-4) and a D-type Flip-Flop. The LUT-4 uses 16 SRAM (static ran-

Figure 2.2: Basic Logic Element (BLE)

Figure 2.3: A Configurable Logic Block (CLB) having four BLEs

dom access memory) bits to implement any 4 inputs boolean function. The output of LUT-4 is connected to an optional Flip-Flop. A multiplexor selects the BLE output to be either the output of a Flip-Flop or the LUT-4.

A Look-Up Table with more number of inputs reduces the total number of LUTs required to map a hardware circuit. More logic functionality can be mapped in a single LUT. This eventually reduces the intercommunication between LUTs, and thus the speed of hardware circuit improves. However, a LUT with more number of inputs increases its area exponentially. [J.Rose et al., 1990] and [E.Ahmed and J.Rose, 2000] have measured the effect of the

Figure 2.4: Switch Block, length 1 wires [G.Lemieux et al., 2004]

number of LUT inputs on area, speed and routability of FPGAs. They have concluded that 4-input LUTs provide a good tradeoff between speed and density of FPGAs.

A CLB can contain a cluster of BLEs connected through a local routing network. Figure 2.3 shows a cluster of 4 BLEs; each BLE contains a LUT-4 and a Flip-Flop. The BLE output is accessible to other BLEs of the same cluster through a local routing network. The number of output pins of a cluster are equal to the total number of BLEs in a cluster (with each BLE having a single output). Whereas the number of input pins of a cluster can be less than or equal to the sum of input pins required by all the BLEs in the cluster. Modern FPGAs contain typically 4 to 10 BLEs in a single cluster.

#### 2.1.2 Routing Network

The routing network of an FPGA occupies 80-90% of FPGA chip area, whereas the logic area occupies only 10-20% area [Betz et al., 1999]. The flexibility of an FPGA is mainly dependent on its programmable routing network. A mesh-based FPGA routing network consists of horizontal and vertical routing tracks which are interconnected through switch boxes (SB). Logic blocks are connected to the routing network through connection boxes (CB). The flexibility of a connection block (Fc) is the number of routing tracks of adjacent channel which are connected to the pin of a block. The connectivity of input pins of logic blocks with the adjacent routing channel is called as Fc(in); the connectivity of output pins of the logic blocks with the adjacent routing channel are connected to the input pin of the logic block. An Fc(in) equal to 0.5 means that only 50% tracks of the adjacent routing channel are connected to the input pin.

Figure 2.5: Channel segment distribution

The flexibility of switch box (Fs) is the total number of tracks with which every track entering in the switch box connects to. The routing tracks connected through a switch box can be bidirectional or unidirectional (also called as directional) tracks. Figure 2.4 shows a bidirectional and a unidirectional switch box having Fs equal to 3. The input tracks (or wires) in both these switch boxes connects to 3 other tracks of the same switch box. The only limitation of unidirectional switch box is that their routing channel width must be in multiples of 2. Multi-length wires are created to reduce area and delay. Figure 2.5 shows an example of different length wires. Longer wire segments span multiple blocks and require fewer switches, thereby reducing routing area and delay. However, they also decrease routing flexibility, which reduces the probability to route a hardware circuit successfully. Modern commercial FPGAs commonly use a combination of long and short wires to balance flexibility, area and delay of the routing network .

Generally, the output pins of a block can connect to any routing track through pass transistors. Each pass transistor forms a tristate output that can be independently turned on or off. However, single-driver wiring technique can also be used to connect output pins of a block to the adjacent routing tracks. For single-driver wiring, tristate elements cannot be used; the output of block needs to be connected to the neighboring routing network through multiplexors in the switch box. Modern commercial FPGA architectures have moved towards using single-driver, directional routing tracks. [G.Lemieux et al., 2004] show that if single-driver directional wiring is used instead of bidirectional wiring, 25% improvement in area, 9% in delay and 32% in area-delay can be achieved. All these advantages are achieved without making any major changes in the FPGA CAD flow.

#### 2.1.3 Software Flow

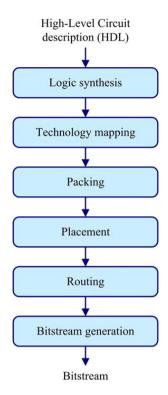

One of the major research aspects of FPGAs is the development of software flow required to map hardware applications on an FPGA. The effectiveness and quality of an FPGA is largely dependent on the software flow provided with an FPGA. The software flow takes an application design description in a Hardware Description Language (HDL) and converts it to a stream of bits that is eventually programmed on the FPGA. Figure 2.6 shows a complete software flow for programming an application circuit on a mesh-based FPGA. A brief description of various modules of software flow is described below.

#### Logic synthesis:

Figure 2.6: FPGA software configuration flow

Logic synthesis [Brayton and McMullen, 1982] [Brayton et al., 1990] transforms an HDL description (VHDL or Verilog) into a set of boolean gates and Flip-Flops. The synthesis tools transform the register-transfer-language (RTL) description of a design into a hierarchical boolean network. Various technology-independent techniques are applied to optimize the boolean network. The typical cost function of technology-independent optimizations is the total literal count of the factored representation of the logic function. The literal count correlates very well with the circuit area. Further details of logic synthesis are beyond the scope of this work.

#### Technology mapping:

After logic synthesis, technology-dependent optimizations are performed. These optimizations transform the technology-independent boolean network into a network of gates in the given technology library. The technology mapping for FPGAs transforms the given boolean network to the available set of blocks on an FPGA. For a traditional FPGA architecture, the boolean network is transformed into Look-Up Tables and Flip-Flops. Technology mapping algorithms optimize a given boolean network for a set of different objective functions including depth, area and power. The FlowMap algorithm [J.Cong and Y.Ding, 1994a] is a

Figure 2.7: Bounding box of a hypothetical 6-terminal net [Betz et al., 1999]

widely used academic tool for FPGA technology mapping. FlowMap is able to find a depth-optimal solution in polynomial time. Later versions of FlowMap are further improved to optimize area and runtime of a boolean network while maintaining the same depth [J.Cong and Y.Ding, 1994b] [J.Cong and Y.Hwang, 1995] [J.Cong and Y.Ding, 2000]. The final output of FPGA technology mapping is a network of I/Os, LUTs and Flip-Flops.

#### Packing:

A mesh-based FPGA consists of an array of Configurable Logic Blocks (CLBs). Each CLB consists of a cluster of Basic Logic Elements (BLEs). A BLE consists of a Look-Up Table and a Flip-Flop. The packing phase, also called as clustering phase groups a Look-Up Table and a Flip-Flop in a BLE, and groups different BLEs into a cluster of BLEs. These BLEs or clusters of BLEs can then be directly mapped on the CLBs of an FPGA. The main optimization goal is to cluster the Look-Up Tables, Flip-Flops and BLEs in such a way that inter-cluster communication is minimized. Less inter-cluster communication ensures less routing resource utilization in an FPGA. The final output of packing is a network of I/Os and CLBs.

#### Placement:

The placement algorithm determines the position of CLB and I/O instances in a packed netlist on the respective CLB and I/O blocks on the FPGA architecture. The main goal of placement algorithm is to place connected blocks near each other so that minimum routing resources are required to route their connections. The placement algorithm can also serve to fulfill other architectural or optimization requirements, such as balancing the wire density across FPGA.

Three major types of commonly used placement algorithms include (i) min-cut (partitioning) based placement algorithm [A.Dunlop and B.Kernighan, 1985] [D.Huang and A.Kahng,

1997] (ii) analytical placement algorithm [G.Sigl et al., 1991] [C.J.Alpert et al., 1997], and (iii) simulated annealing based placement algorithm [S.Kirkpatrick et al., 1983] [C.Sechen and A.Sangiovanni-Vincentelli, 1985]. (i) The partitioning based placement approach is generally suitable for hierarchical FPGA architectures. The partitioner is recursively applied to distribute netlist instances between clusters. The aim is to reduce external communication and merge highly connected instances in the same cluster. (ii) Analytical placement algorithms commonly utilize a quadratic wire length objective function. Although, a quadratic objective is only an indirect measure of the wire length; its main advantage is that it can be minimized very efficiently and is thus suitable for handling large problems. A quadratic function does not give the best possible wire length; it is often followed by some local iterative improvement techniques. (iii) The simulated annealing placement algorithm uses the annealing concept for molten metal which is cooled down gradually to produce high quality metal objects. The simulated annealing algorithm is very effective at finding an acceptably good solution in a limited amount of time. This work concentrates on simulated annealing based placement algorithms.

The simulated annealing placement algorithm is good at approximating an acceptable placement solution for a netlist to be placed on an FPGA. A wire length cost function is used to measure the quality of placement. Netlist instances are initially placed randomly on the FPGA. Different instance moves are made to gradually improve the quality of placement. The "temperature" parameter of the algorithm cools down (decreases) systematically. At each temperature step, move operations are performed "Iteration Count" number of times. "Iteration Count" is proportional to the number of instances in a netlist. The main objective function of placer is to achieve a placement having minimum sum of half-perimeters of the bounding boxes of all the nets. Figure 2.7 shows a bounding box of a hypothetical 6-terminal net. An instance is randomly moved from one position to another; the change in the cost function is computed incrementally. If the cost decreases (improves), the move is always accepted. If the cost increases, the move can still be accepted. The probability of accepting a move that increases the cost is high during the initial phase of the algorithm. But this probability decreases gradually, until in the final phase only those moves are accepted which decrease the cost.

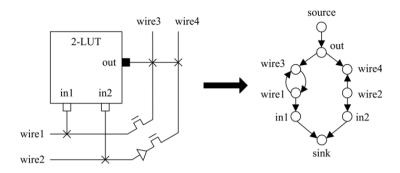

#### Routing:

Once the instances of a netlist are placed on FPGA, connections between different instances are routed using the available routing resources. The FPGA routing problem consists of routing the signals (or nets) in such a way that no more than one signal use the same routing resource. PathFinder [L.McMurchie and C.Ebeling, 1995] routing algorithm is commonly used for FPGAs. In order to perform routing on an FPGA architecture, the routing architecture is initially modeled as a directed graph where different nodes are connected through edges. Each routing wire of the architecture is represented by a node, and connection between two wires is represented by an edge. Figure 2.8 represents a small portion of routing architecture in the form of a directed graph. When a netlist is routed on the FPGA routing graph, each net (i.e connection of a driver instance with its receiver instances) is routed using a congestion driven Dijkstra's "Shortest Path" algorithm [T.Cormen et al., 1990]. Once all nets in a netlist

Figure 2.8: Modeling FPGA architecture as a directed graph [Betz et al., 1999]

are routed, one routing iteration is said to be completed. At the end of an iteration, there can be conflicts between different nets sharing the same nodes. The congestion parameters of the nodes are updated, and routing iterations are repeated until routing converges to a feasible solution (i.e all conflicts are resolved) or routing fails (i.e. maximum iteration count has reached, and few routing conflicts remain unresolved).

#### Bitstream generation:

Once a netlist is placed and routed on an FPGA, bitstream information is generated for the netlist. This bitstream is programmed on the FPGA using a bitstream loader. The bitstream of a netlist contains information as to which SRAM bit of an FPGA be programmed to 0 or to 1. The bitstream generator reads the technology mapping, packing and placement information to program the SRAM bits of Look-Up Tables. The routing information of a netlist is used to correctly program the SRAM bits of connection boxes and switch boxes.

#### 2.2 Research trends in FPGAs

FPGA-based products are very effective for low to medium volume production, they are easy to program and debug, and have less NRE cost and less time-to-market. All these major advantages of an FPGA come through their reconfigurability. However the very same reconfigurability is the major cause of its disadvantages. The flexibility of FPGAs is mainly due to its reprogrammable routing network which takes 80 to 90% of the entire FPGA area [Betz et al., 1999]. The logic area is only 10 to 20% of the FPGA. Due to this reason FPGAs are much larger, slower and more power consuming than ASICs [I.Kuon and J.Rose, 2007]; thus they are unsuitable for high volume production, high performance or low power consumption.

Reconfigurable hardwares and FPGA architectures have many active research domains. A major aspect of research in reconfigurable hardwares revolves around decreasing the drawbacks of FPGAs, with or without compromising upon its major benefits. Following are few of the major tradeoff solutions that have been proposed in solving the area, speed, power and/or volume production problems of FPGAs.

- Hard-Blocks: Logic density of an FPGA is improved by incorporating dedicated hard-blocks in an FPGA. Hard-Blocks, or in other words small ASICs, in FPGAs increase their speed and reduce their overall area and power consumption. Hard-blocks can include multipliers, adders, memories, floating-point units etc. In this regard, [Beauchamp et al., 2006] have introduced embedded floating-point units in FPGAs, [C.H.Ho et al., 2006] have developed virtual embedded block methodology to model arbitrary embedded blocks on existing commercial FPGAs. [Hartenstein, 2001] has presented a brief survey of a decade of R&D on coarse grain reconfigurable hardware and their related compilation techniques. Figure 2.10 shows a commercial FPGA architecture that uses embedded hard-blocks.

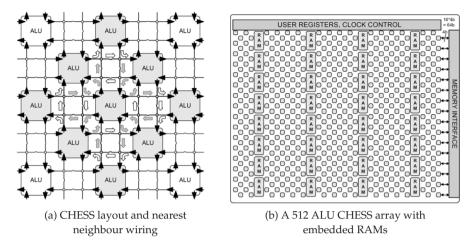

- Application Specific FPGAs: The type of logic blocks and the routing network in an FPGA can be optimized to gain area and performance advantages for a given application domain (controlpath-oriented applications, datapath-oriented applications, etc). These types of FPGAs may include different variety of desired hard-blocks, appropriate amount of flexibility required for the given application domain or bus-based interconnects rather than bit-based interconnects. [Marshall et al., 1999] have presented a reconfigurable arithmetic array for multimedia applications, [Verma and Akoglu, 2007] have presented a coarse grained reconfigurable architecture for variable block size motion estimation and, [Ye and Rose, 2006] have used bus-based connections to improve density of FPGAs for datapath circuits. Figure 2.14 shows a reconfigurable arithmetic array for multimedia applications.

- FPGA to Structured-ASIC: The ease of designing and prototyping with FPGAs can be exploited to quickly design a hardware application on an FPGA. Later, improvements in area, speed, power and volume production can be achieved by migrating the application design from FPGA to other technologies such as Structured-ASICs. In this regard, Alter provides a facility to migrate its Stratix IV based application design to HardCopy IV [HardCopy, IV]. The eASIC Nextreme [eASIC, 2010] uses an FPGAlike design flow to map an application design on SRAM programmable LUTs, which are later interconnected through mask programming of few upper routing layers. cA-SIC [Compton and Hauck, 2007] explores the design space between ASIC and FPGA; configurable ASIC cores are designed to execute a given set of application designs at exclusive times. Tierlogic [TIERLOGIC, 2010] is a recently launched FPGA vendor that offers 3D SRAM-based TierFPGA devices for prototyping and early production. The same design solution can be frozen to a TierASIC device with one low-NRE custom mask for error-free transition to an ASIC implementation. The SRAM layer is placed on an upper 3D layer of TierFPGA. Once the TierFPGA design is frozen, the bitstream information is used to create a single custom mask metal layer that will replace the SRAM programming layer.

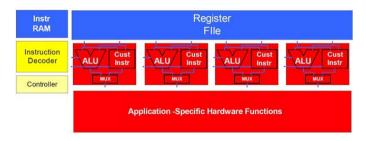

- FPGA with processors: A considerable amount of FPGA area can be saved by implementing the control path portion of a circuit on a microprocessor, and only the compute intensive datapath portion of a circuit is implemented on FPGAs. An FPGA is connected to a microprocessor in different ways (i) A soft processor is implemented on

FPGA reconfigurable resources (like shown in [NIOS, II], [MicroBlaze, 2010] and [Peter Yiannacouras and Rose, 2007]), (ii) a processor is incorporated in an FPGA as a dedicated hard-block (like AVR Processor integrated in Atmel FPSLIC [ATMEL, 2010] or PowerPC processors embedded in Xilinx Virtex-4 [Xilinx, 2010]), or (iii) an FPGA is attached with the pipeline of a processor to execute customized hardware instructions (like [Callahan et al., 2000] and [Jones et al., 2005]). Figure 2.13 illustrates a VLIW processor that supports application-specific hardware instructions.

- Time-multiplexed signals: Instead of using a dedicated routing track for routing a single signal, a routing wire is time-multiplexed and used by different signals at different times [Kapre et al., 2006] [Essen et al., 2009]. In this way, considerable amount of routing resources can be reduced to achieve area gains. Time multiplexing is handled by adding special hardware circuitry. These extra resources make time-multiplexing less attractive for commercial FPGA architectures where generally single-bit routing wires are used. However, these extra resources can be amortized across word-wide routing resources in coarse-grained reconfigurable arrays.

- Time-multiplexed FPGAs: The capacity or logic density of FPGAs is increased by executing different portions of a circuit on an FPGA in a time multiplexing mode [Trimberger et al., 1997] [Miyamoto and Ohmi, 2008]. An application design is divided into different sub-circuits, and each sub-circuit runs as a individual context of FPGA. The state information of each sub-circuit is saved in context registers before a new context runs on FPGA. Tabula [Tabula, 2010] is a recently launched FPGA vendor that provides time-multiplexed FPGAs.

The following section discusses different case-studies employing one of the above techniques.

# 2.2.1 Versatile Packing, Placement and Routing, VPR

Versatile Packing, Placement and Routing for FPGAs (commonly known as VPR) [V.Betz and J.Rose, 1997] [Betz et al., 1999] [A.Marquart et al., 1999] is the most widely used academic mesh-based FPGA exploration environment. It allows to explore mesh-based FPGA architectures by employing an empirical approach. Benchmark circuits are technology mapped, placed and routed on a desired FPGA architecture. Later, area and delay of FPGAs are measured to determine best architectural parameters. Different CAD tools in VPR are highly optimized to ensure high quality results; as poor CAD tools may lead to inaccurate architectural conclusions. Area and delay models are sufficiently accurate to compare the effect of different architectural changes.

The GILES project (Good Instant Layout of Erasable Semiconductors) [Padalia et al., 2003] [Kuon et al., 2005] generates the physical layout of an FPGA from the architecture specifications given as input to VPR. Developing a new FPGA is a challenging and time-consuming task. [Padalia et al., 2003] report that the creation of new FPGA requires 50 to 200 person years;

Figure 2.9: A Heterogeneous FPGA in VPR 5.0 [Luu et al., 2009]

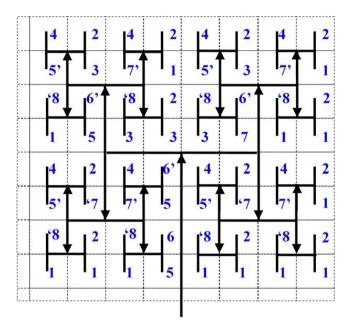

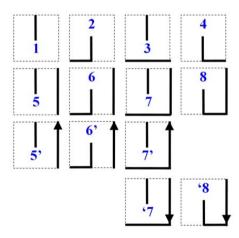

thus increasing the overall time-to-market. It is thus an interesting option to significantly reduce the time-to-market of FPGAs at the expense of limited area penalty. GILES automatically generates a transistor-level schematic of an FPGA tile from a high-level architectural specification. The output of GILES is a mask-level layout of a single tile that can be replicated to form an FPGA array.

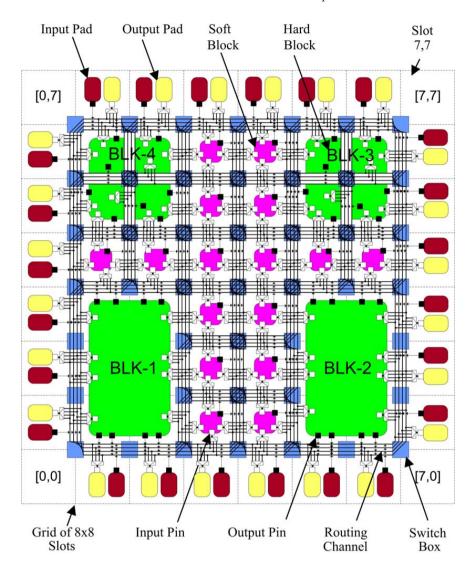

The latest version of VPR known as VPR 5.0 [Luu et al., 2009] supports hard-blocks (such as multiplier and memory blocks) and single-driver routing wires. Hard-blocks are restricted to be in one grid width column, and that column can be composed of same type of blocks. The height of a block must be an integral number of grid units. In case a block height is indivisible with the height of FPGA, some grid locations are left empty. Figure 2.9 illustrates a heterogeneous FPGA with 8 different kinds of blocks. VPR 5.0 also provides optimized electrical models for a wide range of architectures for different process technologies.

# 2.2.2 Madeo, a framework for exploring reconfigurable architectures

Madeo [Lagadec, 2000] is a design suite for the exploration of reconfigurable architectures. It includes a modeling environment that supports multi-grained, heterogeneous architectures with irregular topologies. Madeo framework initially allows to model an FPGA architecture. The architecture characteristics are represented as a common abstract model. Once the architecture is defined, the CAD tools of Madeo can be used to map a target netlist on the architecture. Madeo embeds placement and routing algorithms (the same as used by VPR [V.Betz and J.Rose, 1997]), a bitstream generator, a netlist simulator, and a physical layout generator. Madeo supports architectural prospection and very fast FPGA prototyping. Several FPGAs, including some commercial architectures (such as Xilinx Virtex family) and prospective ones (such as STMicro LPPGA) have been modeled using Madeo. The physical layout is produced as VHDL description.

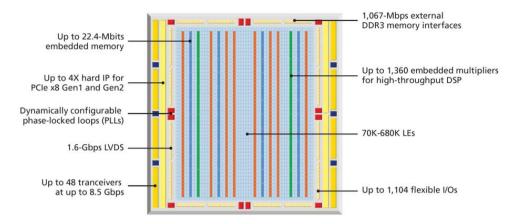

#### 2.2.3 Altera Architecture

Altera's Stratix IV [Stratix, IV] is a mesh-based FPGA architecture family fabricated in 40-nm process technology. Figure 2.10 shows the global architectural layout of Statix IV. The logic structure consists of LABs (Logic Array Blocks), memory blocks and digital signal processing (DSP) blocks. LABS are distributed symmetrically in rows and columns and are used to implement general purpose logic. The DSP blocks are used to implement full-precision multipliers of different granularities. The memory blocks and DSP blocks are placed in columns at equal distance with one another. Input and Output (I/Os) are located along the periphery of the device.

Logic array blocks (LABs) and adaptive logic modules (ALMs) are the basic building blocks of the Stratix VI device. They can be used to configure logic functions, arithmetic functions, and register functions. Each LAB consists of ten ALMs, carry chains, arithmetic chains, LAB control signals, local interconnect, and register chain connection lines. The internal LAB structure is shown in Figure 2.11. The local interconnect connects the ALMs belonging to the same LAB. The direct link allows a LAB to drive into the local interconnect of its left or right neighboring LAB. The register chain connects the output of ALM register to the adjacent ALM register in the LAB. A memory LAB (MLAB) is a derivative of LAB which can be either used just like a simple LAB, or as a static random access memory (SRAM). Each ALM in an MLAB can be configured as a 64x1, or 32x2 blocks, resulting in a configuration of 64x10 or 32x20 simple dual-port SRAM block. MLAB and LAB blocks always coexist as pairs in Stratix IV families.

The DSP blocks in Stratix IV are optimized to support signal processing applications such as Finite Impulse Response (FIR), Infinite Impulse Response (IIR), Fast Fourier Transform functions (FFT) and encoders etc. Stratix IV device has two to seven columns of DSP blocks that can implement multiplication, multiply-add, multiply-accumulate (MAC) and dynamic arithmetic or logical shift functions. The DSP block supports 9x9, 12x12, 18x18 and 36x36 multiplication operations. The Statix IV devices contain three different sizes of embedded SRAMs. The memory sizes include 640-bit memory logic array blocks (MLABs), 9-Kbit M9K blocks, and 144-Kbit M144K blocks. The MLABs have been optimized to implement filter delay lines, small FIFO buffers, and shift registers. M9K blocks can be used for general purpose memory applications, and M144K are generally meant to store code for a processor, packet buffering or video frame buffering.

# 2.2.4 Altera HardCopy

Altera gives provision to migrate FPGA-based applications to Structured-ASIC. Their Structured-ASIC is called as HardCopy [HardCopy, IV]. The main theme is to design, test and even initially ship a design using an FPGA. Later, the application circuit that is mapped on the FPGA can be seamlessly migrated to HardCopy for high volume production. Their latest HardCopy-IV devices offer pin-to-pin compatibility with the Stratix IV prototype, making

Figure 2.10: Stratix IV architectural elements

Figure 2.11: Stratix IV LAB Structure

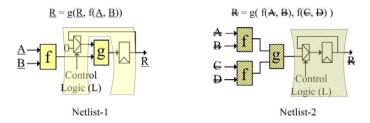

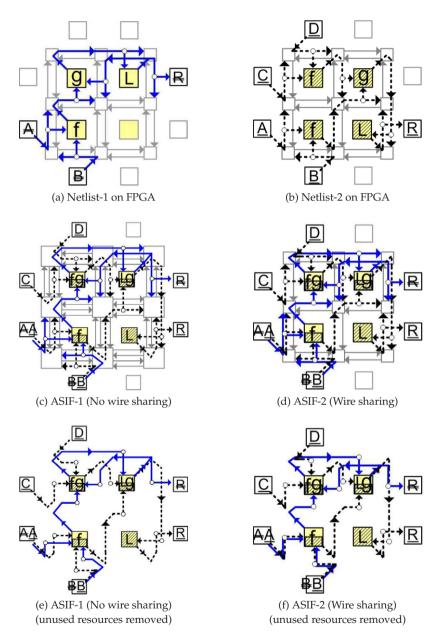

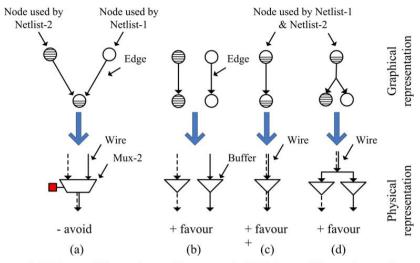

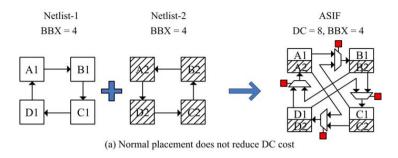

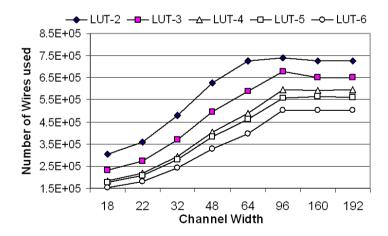

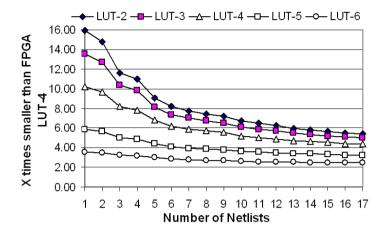

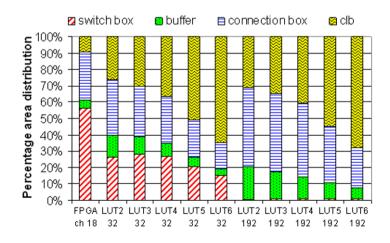

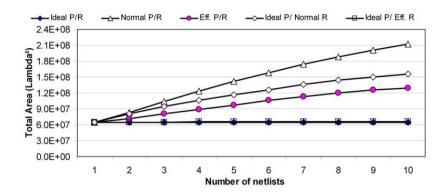

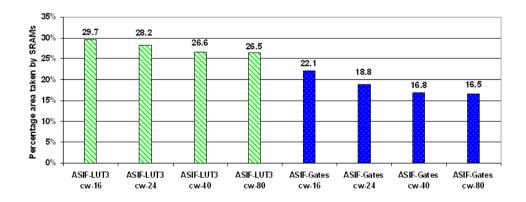

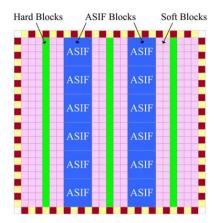

Figure 2.12: FPGA/Structured-ASIC (HardCopy) Correspondence [Hutton et al., 2006]